Simulation scheme for CMOS logic gates with input pulse forming and... | Download Scientific Diagram

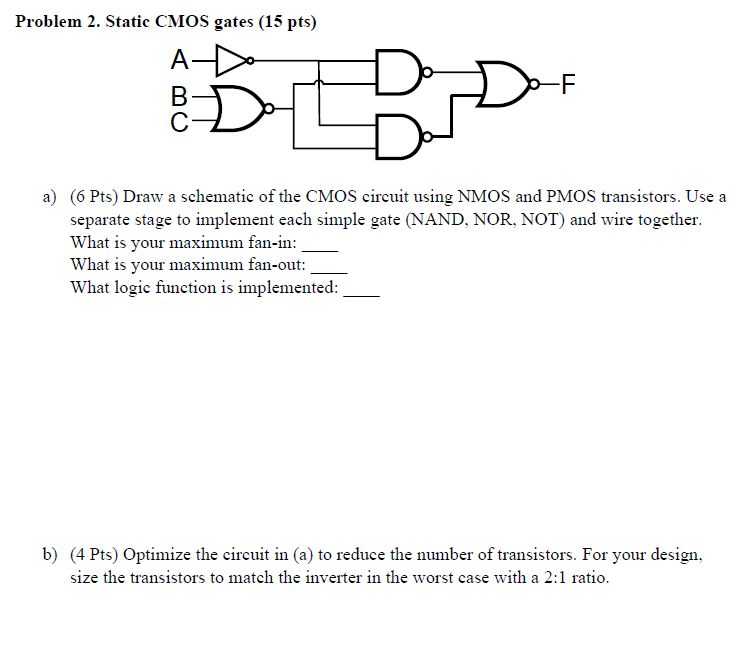

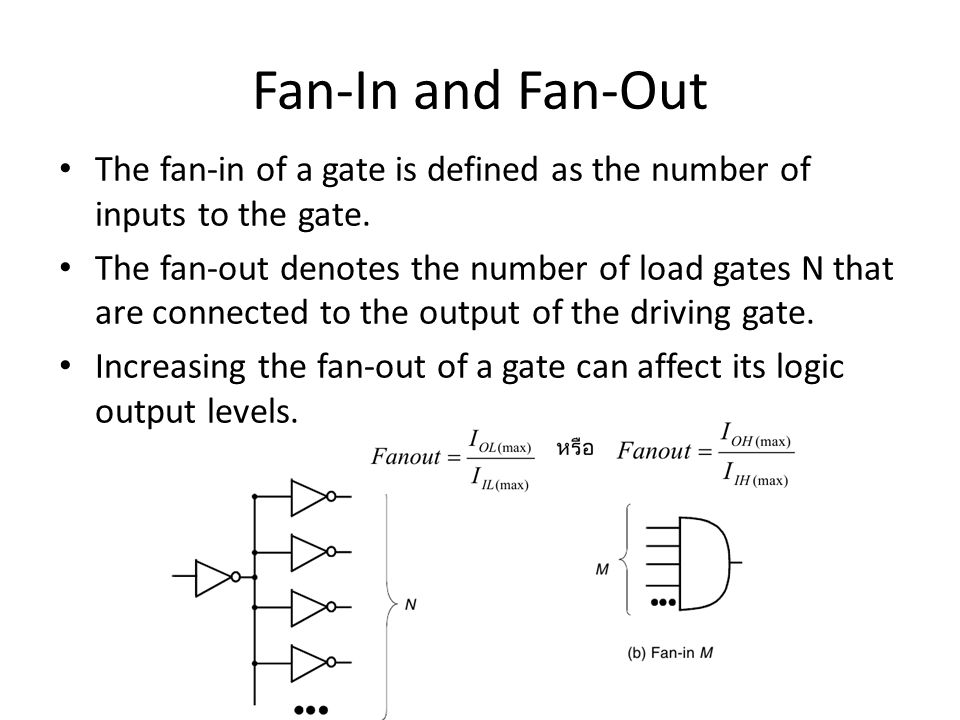

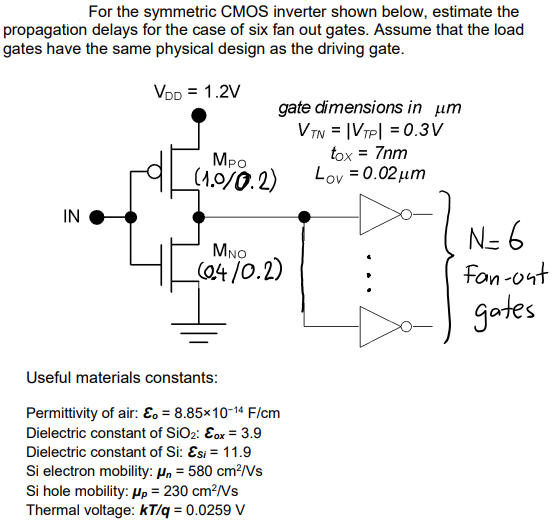

Exercises S1 1. (a) Is it ever possible for the voltage ranges of logical 0 and logical 1 to overlap, as shown below? (b) What disadvantage would accure from restricting the logic ranges to the far corners of the possible voltage range of the chip? 2. A weak ...

![The Stuff Dreams Are Made Of [Part 2] The Stuff Dreams Are Made Of [Part 2]](http://www.realworldtech.com/includes/images/articles/cmosintro2-fig3.gif?x56147)